Cccu Cu Ccpolymer Cu Hybrid Bonding O Ith Iuo µyao Nucuonoo Uo O Eµec 3dic Lab

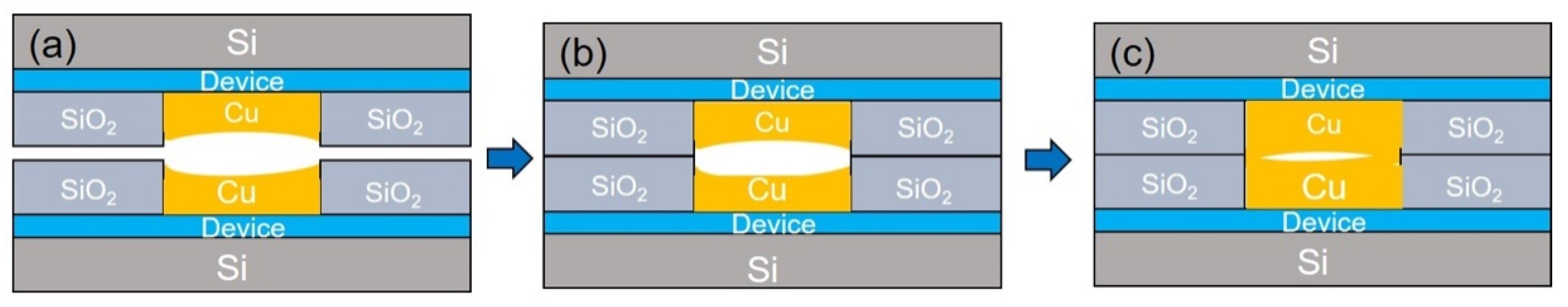

Next Generation Hybrid Bonding Irt Nanoelec Accordingly, based on the progress of low temperature cu cu bonding, low temperature cu sio 2 hybrid bonding will be introduced as an emerging bonding technology to solve the coplanarity and filling issue, which can provide the great potential for 3d integration with ultra high density of interconnection. Hybrid bonding enables the commercialization of ultra fine pitch high density 3d packages. cu sio 2 hybrid bonding is the standard packing interface recently introduced in the industry. herein, the cu polymer hybrid bonding interface beyond cu sio 2 is proposed in order to have high compatibility for additional processes in the future. ideally.

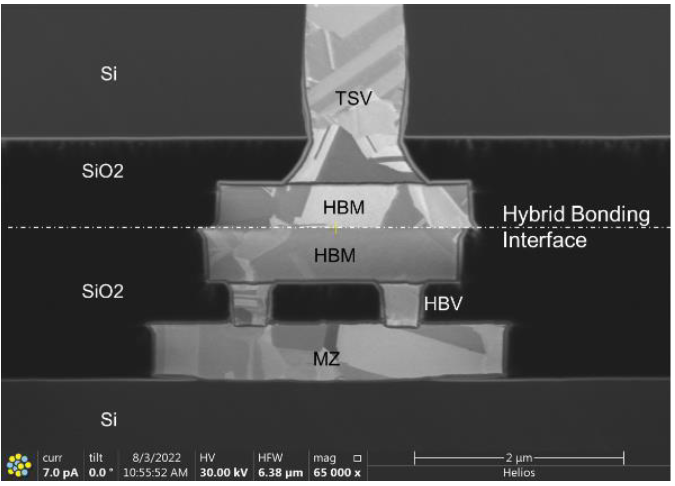

Materials Free Full Text Low Temperature Cu Sio2 Hybrid Bonding Wafer to wafer hybrid bonding is an attractive 3d integration technology for stacking multiple heterogeneous chips with high 3d interconnect density. we highlight recent design and technology. After having successfully demonstrating a 2 layer face to back (f2b) test vehicle (tv), we reached the next level of integration by achieving a 3 layer tv with fine pitch cu cu hybrid bonding (hb) technology and high density (hd) through silicon via (tsv). different cu damascene levels that simulate back end of line (beol) layers are used on 300mm wafers to fabricate the 3 layer tv. after. Among various bonding technologies, bumpless cu based hybrid bonding has become the main solution to the requirement of high speed and density. this talk will introduce the platform, current status, and corresponding applications of hybrid bonding. in addition, high bonding temperature with the induced thermal stress and warpage needs to be solved. 3dic lab is led by prof. kuan neng chen. our research topics include three dimensional integrated circuits (3d ic), heterogeneous integration, and advanced packaging technology. as the scaling of transistor size faces its physical limits, 3d ic becomes the mainstream candidate to extend “moore’s law” and fulfill “more than moore” applications. our vision is to demonstrate a highly.

Comments are closed.