Github Ieee Nitk Parallelizing Fft A Parrallelized Implementation Of

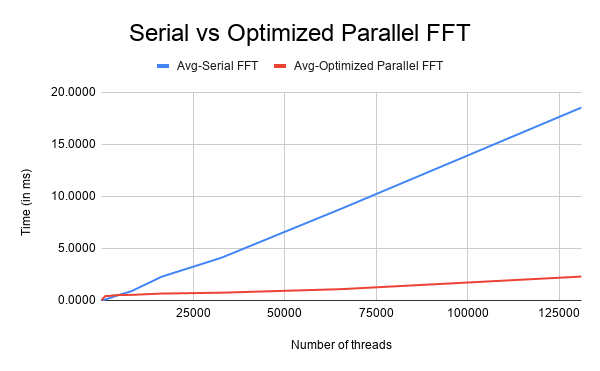

Github Ieee Nitk Parallelizing Fft A Parrallelized Implementation Of A parrallelized implementation of fft algorithm using cuda github ieee nitk parallelizing fft: a parrallelized implementation of fft algorithm using cuda. The balancing factor is a function of n with a half and half split of \(\left \lfloor{\sqrt{n}}\right \rfloor\). for 2d inputs, the 1d fft is applied to both row and column of the input. each row of the input sequence is parallelized and a transpose of the matrix is parallelized in a similar manner.

Virtual Expo Ieee Nitk A parrallelized implementation of fft algorithm using cuda packages · ieee nitk parallelizing fft. The fast fourier transform (fft) with a focus on improving its memory bandwidth usage using openmp. for this project, we implemented parallel versions of 1d discrete fourier transform (dft), 1d recursive fft, 1d iterative fft, and 2d fft using our iterative 1d fft; we also implemented several optimizations for these implementations. This was easily parallelized by parallelizing each dot product. we were able to significantly optimize this by noticing only n elements of the matrix actually needed to be computed (rather than n 2) and precomputing them in parallel. recursive fft: this started as the textbook recursive implementation of the cooley tukey algorithm. In this paper we discuss the vlsi implementation of the new radix 2 decimation in time (dit) fast fourier transform (fft) algorithm with reduced arithmetic complexity which is based on scaling the twiddle factor. some signal processing require high performance fft processors and to meet these performance requirements, the processor needs to be pipelined and parallelized. an optimized asic.

Virtual Expo Ieee Nitk This was easily parallelized by parallelizing each dot product. we were able to significantly optimize this by noticing only n elements of the matrix actually needed to be computed (rather than n 2) and precomputing them in parallel. recursive fft: this started as the textbook recursive implementation of the cooley tukey algorithm. In this paper we discuss the vlsi implementation of the new radix 2 decimation in time (dit) fast fourier transform (fft) algorithm with reduced arithmetic complexity which is based on scaling the twiddle factor. some signal processing require high performance fft processors and to meet these performance requirements, the processor needs to be pipelined and parallelized. an optimized asic. This paper considers the automatic generation of parallelized fast fourier transform (fft) logic for field programmable gate array (fpga) chips. a custom software tool has been created to generate vhdl logic descriptions for parallelized radix 4 fft architectures using decimation in frequency (dif). these architectures accept n simultaneously provided fixed point complex valued input samples. Follow their code on github. parallelizing fft parallelizing fft public. forked from ieee nitk parallelizing fft. a parrallelized implementation of fft algorithm.

Comments are closed.