Memory Interfacing Designing The 8086 Cpu Module Microprocessor

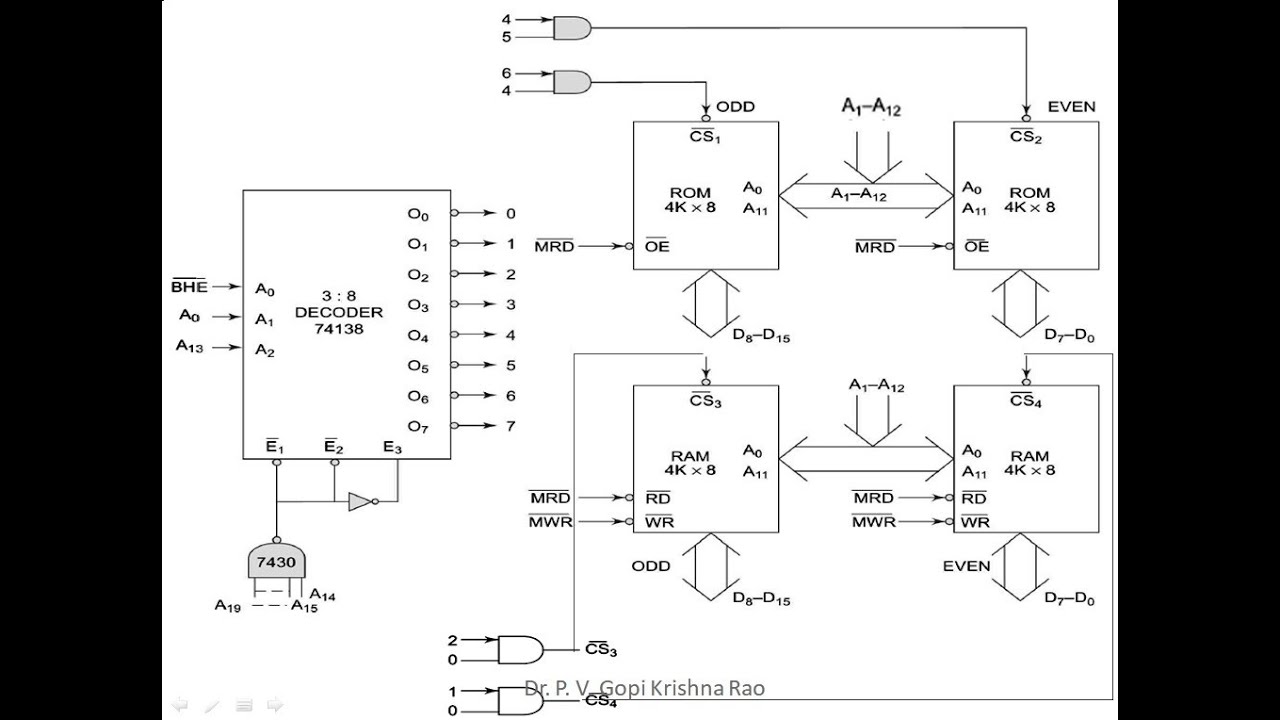

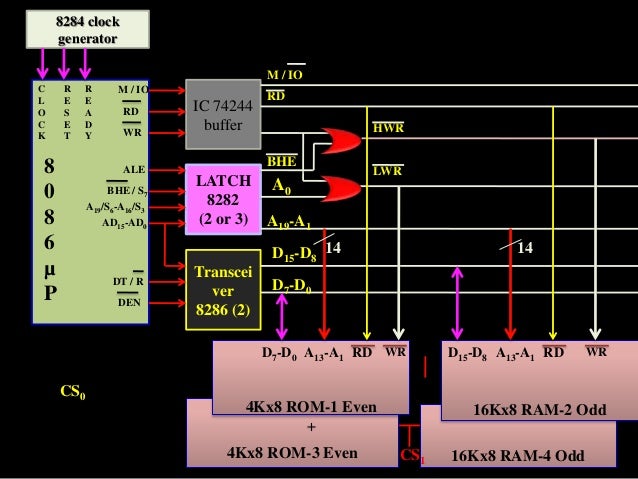

Memory Interfacing With 8086 Microprocessor Youtube The intricacies of interfacing memory with 8086 or 80286 processors reveal the nuanced challenges and solutions in microprocessor based system design. these processors, with their 16 bit data buses, necessitate a division of memory into even and odd banks to manage data flow efficiently. Module 7: memory interfacing. q1. an 8086 based system has the following memory requirements: 256k of ram from 60000h. 64k rom 8, 64k ram 4, ls138 2. design the memory interfacing circuit. q2. for an 80286 processor that has 16 mb of memory of which 4m is rom and the rest is ram. half of the rom mapped to address space starting at 00 00 00h.

Memory Interfacing In 8086 Youtube Discover the intricate world of memory interfacing and the art of designing the 8086 cpu module in this insightful video on microprocessor & application. unc. To illustrate memory interfacing, consider connecting 2k (2048 bytes) memory chips to the 8088 processor to achieve a total memory of 8kb (8192 bytes). this scenario involves calculating the required number of chips, designing a memory map that assigns address ranges to each chip, and developing address decoding logic to select the appropriate. The following block diagram explains the refreshing logic and 8086 interfacing with dynamic ram. each chip is of 16k * 1 bit dynamic ram cell array. the system contains two 16k byte dynamic ram units. all the address and data lines are assumed to be available from an 8086 microprocessor system. The 8088 and 8086 microprocessors,triebel and singh 21 introduction 8.1 8088 and 8086 microprocessors 8.2 minimum mode and maximum mode systems 8.3 minimum mode interface 8.4 maximum mode interface 8.5 electrical characteristics 8.6 system clock 8.7 bus cycles and time states 8.8 hardware organization of the memory address space—.

Interfacing Memory With 8086 Microprocessor The following block diagram explains the refreshing logic and 8086 interfacing with dynamic ram. each chip is of 16k * 1 bit dynamic ram cell array. the system contains two 16k byte dynamic ram units. all the address and data lines are assumed to be available from an 8086 microprocessor system. The 8088 and 8086 microprocessors,triebel and singh 21 introduction 8.1 8088 and 8086 microprocessors 8.2 minimum mode and maximum mode systems 8.3 minimum mode interface 8.4 maximum mode interface 8.5 electrical characteristics 8.6 system clock 8.7 bus cycles and time states 8.8 hardware organization of the memory address space—. Chapter 7 memory system design. Lecture 13 memory interface. memory interfacing is an essential topic for digital system design. in fact the among silicon area devoted to memory in a typical digital embedded system or a computer system is substantial. for example, in a mobile phone, the number of transistors devoted to memory is many times more than those used for computation.

Comments are closed.