Plot Of Cu Seed Barrier Layer Thickness At Via Bottom With Varying

Plot Of Cu Seed Barrier Layer Thickness At Via Bottom With Varying Figure 2 is a plot of the copper seed barrier layers sputtered thickness and the tapered via profile with varying taper etch time. the longer the taper etch time, the wider the degree of tapering. It can achieve the deposition of a continuous metal layer into high ar microvias. a 0.2 μm thick titanium layer as a barrier and adhesion layer and a 0.5 μm thick copper seed layer are deposited into the vertical deep vias by electron beam evaporation using sccot 380 equipment. the electron beam evaporation parameters are summarised in table.

Barrier Layer Of Cu Interconnects Encyclopedia Mdpi This letter presents a new strategy for the formation of continuous cu seed layer in high aspect ratio (har) through silicon vias (tsvs) with large depth based on sequential sputtering and electroless plating. the deposited seed layer is continuous and dense even at the bottom of the tsvs, which is difficult to achieve by individual sputtering or electroless plating. combined with the spin. Cu alloy seed was later developed to increase em life time. cual alloy can. retard cu migration at the grain boundary and interface; cumn alloy can create a. self formed barrier. co wetting and capping layers are the newest approaches for. suppressing em failures at 32nm and below. By controlling the peald cycle, a cu seed layer of 5–7 nm thickness was deposited on the side wall of a trench. the cu seed layer formed at 150 °c (fig. 6 (a)) was continuous, and had enough conductivity to achieve efficient filling using a conventional ecp solution. The minimum thickness of the cu seed layer inside tsvs is around 100 nm, and such a continuous seed layer is beneficial to the subsequent electroplating of cu conductor. the proposed process flow for the formation of liner, barrier and seed layer in ultra high aspect ratio tsvs is useful for the fabrication of interconnects in heterogeneous.

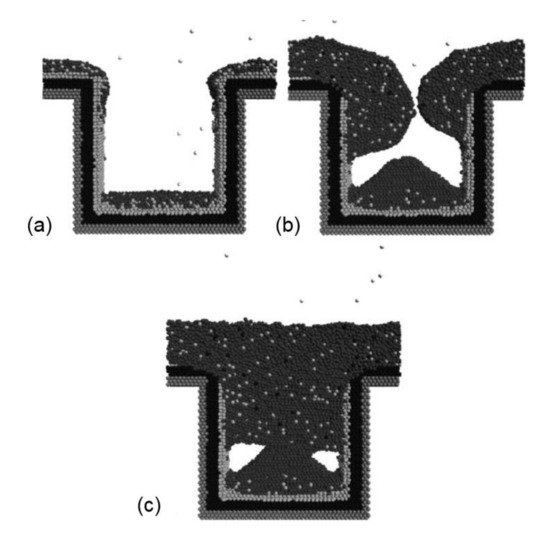

A Schematic Diagram Of A Seed Coated First With A Seed Barrier By controlling the peald cycle, a cu seed layer of 5–7 nm thickness was deposited on the side wall of a trench. the cu seed layer formed at 150 °c (fig. 6 (a)) was continuous, and had enough conductivity to achieve efficient filling using a conventional ecp solution. The minimum thickness of the cu seed layer inside tsvs is around 100 nm, and such a continuous seed layer is beneficial to the subsequent electroplating of cu conductor. the proposed process flow for the formation of liner, barrier and seed layer in ultra high aspect ratio tsvs is useful for the fabrication of interconnects in heterogeneous. The copper electrochemical deposition (cu ecd) filling capability of high aspect ratio through silicon vias (har tsvs) and homogeneity over 300 mm wafers were investigated on a film stack of thermal ald (thald) ta x n y barrier with thermal ald ru seed in comparison to ti x n y barrier with a standard cu i pvd seed layer using a commercial 300 mm plating tool. For the evaluation of the different seed layers two different test masks for 200 mm wafer have been used for the via formation. the first one (mask 1), which was used for most seed layers.

Comments are closed.